## **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>6</sup>: G11C 29/00

(11) International Publication Number:

WO 97/34300

A1 |

(43) International Publication Date:

18 September 1997 (18.09.97)

(21) International Application Number:

PCT/US96/03443

(22) International Filing Date:

13 March 1996 (13,03,96)

- (71) Applicant (for all designated States except US): MEMSYS LTD. [IL/IL]; 21 HaVaad HaLeumi Street, P.O. Box 16031, 91160 Jerusalem (IL).

- (71)(72) Applicant and Inventor: COEL, Craig [US/IL]; 8/2 Ben Sruk Street, 92309 Jerusalem (IL).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): FRIEDMAN, Yaakov [IL/IL]; 111 Uziel Street, 96431 Jerusalem (IL). SHNAIDER, Mark [IL/IL]; 51b Tchernachovski Street, 92587 Jerusalem (IL). SUTSKEVER, Efim [IL/IL]; 2/11 Itshak Tunik Street, 97795 Jerusalem (IL).

- (74) Agents: GALLOWAY, Peter, D.; Ladas & Parry, 26 West 61st Street, New York, NY 10023 (US) et al.

(81) Designated States: AL, AM, AT, AU, AZ, BB, BG, BR, BY, CA, CH, CN, CZ, DE, DK, EE, ES, FI, GB, GE, HU, IS, JP, KE, KG, KP, KR, KZ, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, TJ, TM, TR, TT, UA, UG, US, UZ, VN, ARIPO patent (KE, LS, MW, SD, SZ, UG), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG).

### **Published**

With international search report.

(54) Title: APPARATUS AND METHOD FOR UTILIZING NONPERFECT MEMORY ELEMENTS

#### (57) Abstract

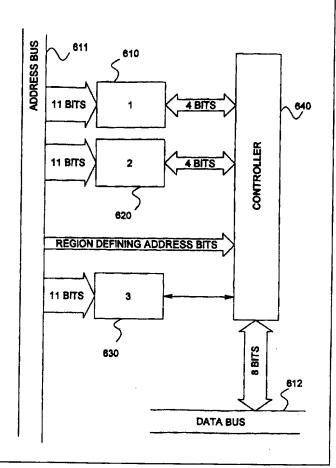

Memory apparatus serving a data supplying device, the memory apparatus including a plurality of at least n+1 memory elements (610-630), each memory element including a multiplicity of memory cells, wherein at least one memory cell in at least one of the n+1 memory elements (610-630) is defective, and a defective memory element controlling device (640) operative to control the plurality of memory elements including a least one defective memory element so as to obtain timing at least as rapid as the timing of a plurality of n perfect memory elements without providing additional physical connections to the data supplying device.